# CONVERTIDORES D/A y A/D

MANTENIMIENTO ELECTRÓNICO

#### SISTEMA PROCESADO DIGITAL

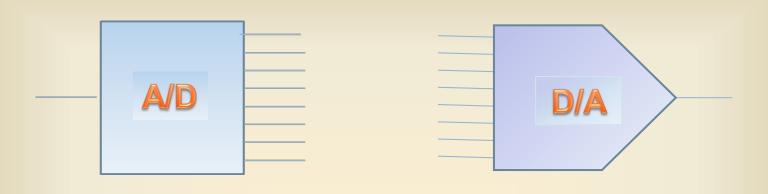

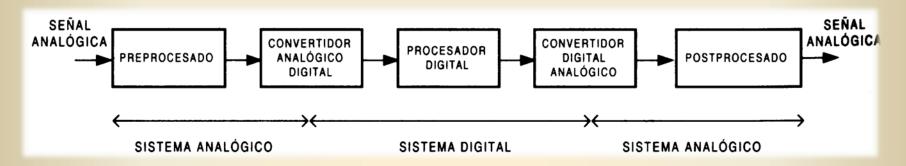

Las ventajas de trabajar en el mundo digital son evidentes: Ausencia de ruido, fácil procesamiento y facilidad de almacenamiento.

Sin embargo las magnitudes físicas de la naturaleza como temperatura, humedad, longitud, intensidad de luz, sonido, etc., son analógicas.

Para poder procesar de forma digital estas variables naturales hace falta un convertidor analógico a digital.

Una vez procesadas las señales, puede ser necesario pasarlos al mundo analógico para poder ser útiles para nosotros, como el sonido; en este caso será necesario un convertidor de digital a analógico.

- 1. CONVERTIDORES DIGITAL-ANALÓGICO D/A

- **1. FUNCIÓN DE TRANSFERENCIA**

- O 2. CARACTERÍSTICAS

- TIPOS Y APLICACIONES

- 2. CONVERTIDORES ANALÓGICO-DIGITAL A/D

- O 1. FUNCIÓN DE TRANSFERENCIA

- O 2. CARACTERÍSTICAS

- TIPOS Y APLICACIONES

- O 4. PROCESO DE CONVERSIÓN

- 3. O CRITERIOS DE SELECCIÓN

El número expresado en binario natural de n bits:

$$b_{n-1} b_{n-2} \dots b_3 b_2 b_1 b_0$$

Representa en decimal el valor B, tal que:

$$B = b_{n-1}^{2^{n-1}} + b_{n-2}^{2^{n-2}} + \dots + b_3^{2^3} + b_2^{2^2} + b_1^{2^1} + b_0^{2^0}$$

Normalizando respecto a 2<sup>n</sup>

$$D = B/2^{n} = b_{n} 2^{-1} + b_{n-1} 2^{-2} + \dots + b_{3} 2^{-n+3} + b_{2} 2^{-n+2} + b_{1} 2^{-n+1} + b_{0} 2^{-n}$$

**D** = Valor binario fraccional

$$0 \le D \le (1 - 2^{-n}); 0 \le D \le (\approx 1)$$

El incremento mínimo posible es 2<sup>-n</sup> = 1/2<sup>n</sup>

#### CONVERSIÓN DIGITAL A ANALÓGICA

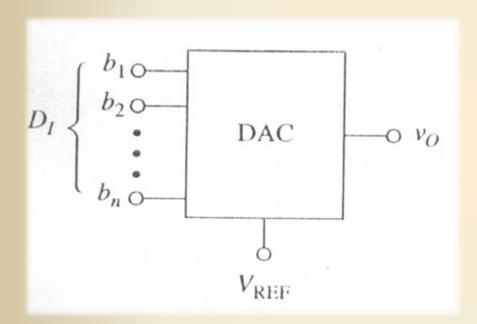

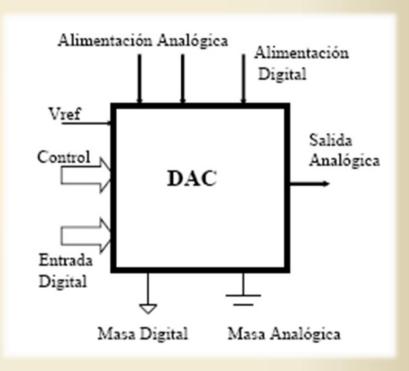

El valor de la salida de un convertidor digital—analógico dependerá del valor digital introducido en la entrada, de la tensión de alimentación del circuito (que sirve de límite), del tipo de circuito, unipolar o bipolar, de una constante de conversión "k", y de las tensiones de referencia positiva y negativa analógicas introducidas.

Cuando en la entrada todos los bits son **0** tendremos el mínimo valor de salida posible.

Cuando en la entrada todos los bits son 1 tendremos el máximo valor de la salida.

$$V_0 = k \cdot (Vref^- + D \cdot (Vref^+ - Vref^-))$$

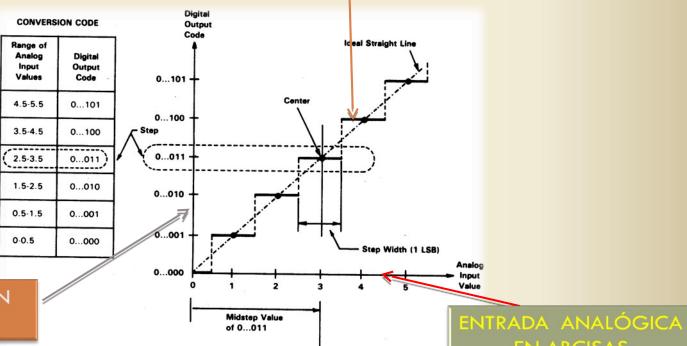

A/D DIA F. TRANSFERENCIA D/A Analog Output Value SALIDA ANALÓGICA Ideal Straight Line **EN ORDENADAS** 5 Step Height (1 LSB) 3 2 Step Value Digital Input Code 0...010 0...011 0...100 0...101 0...001

**CONVERSION CODE**

| Digital Input Code  | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 |

|---------------------|------|------|------|------|------|------|

| Analog Output Value | 0    | 1    | 2    | 3    | 4    | 5    |

Step

ENTRADA DIGITAL EN ABCISAS

- Resolución

- Precisión de la conversión

- Rango dinámico de entrada

- Rango dinámico de salida

- Modo de funcionamiento v,i

- Unipolar o bipolar

Tiempo de conversión

**Glitcher**

**Error de offset**

Error de ganancia

Sensibilidad a la temperatura

**Monotonicidad**

Error de no linealidad Integral Diferencia

# RESOLUCIÓN

Al máximo rango de salida posible se llama rango de fondo de escala.

En el caso que la termión de referencia negativa sea 0, es común hablar de tensión de fondo de escala:

La **apreciación** en <u>mínimur inf</u>remento posible, esto es, el incremento del valor de la salida que produce el bit menos significativo:

La **resolución** es el número de bit les entrada. La apreciación es mejor (valor más bajo) cuantos más bits tenga.

#### CARACTERÍSTICAS DE LOS DACS

D/A

La precisión viene determinada por el conjunto de errores que se pueden producir durante la conversión.

Suele expresarse en número de bits menos significativos. Es típico que los fabricantes nos digan que la precisión es de ½ o 1LSB.

Rango dinámico de entrada 20·log2<sup>n</sup> (dB)

Rango dinámico de salida 20.logVfSR (dB)

### CARACTERÍSTICAS DE LOS DACS

**Modo de funcionamiento v, i**. Expresa si la salida es en forma de tensión o en forma de corriente.

Unipolar o bipolar. Indica que la salida actúa en un solo cuadrante, unipolar (sólo da valores positivos o sólo valores negativos) o actúa en dos cuadrantes, bipolar (puede dar valores positivos y negativos)

**Tiempo de conversión**. No suele ser un valor relevante, aunque en algún caso deba ser tenido en cuenta.

Glitchers son picos de señal que aparecen en la salida debidos a retardos cuando cambian los valores de las entradas.

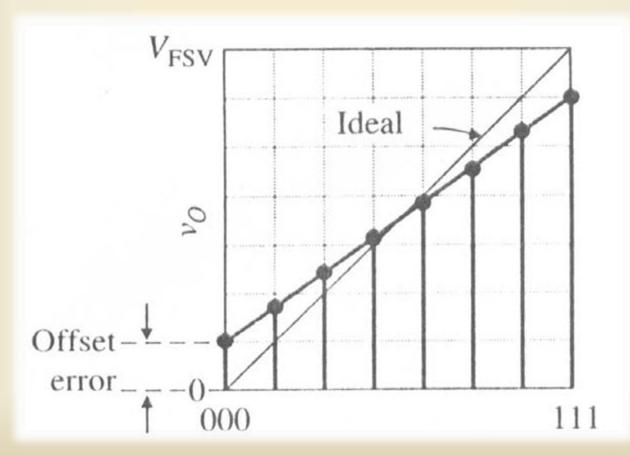

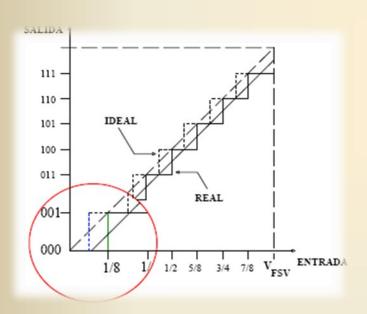

# ERROR DE OFFSET

D/A

Es el error de 0.

**CONVERTIDORES**

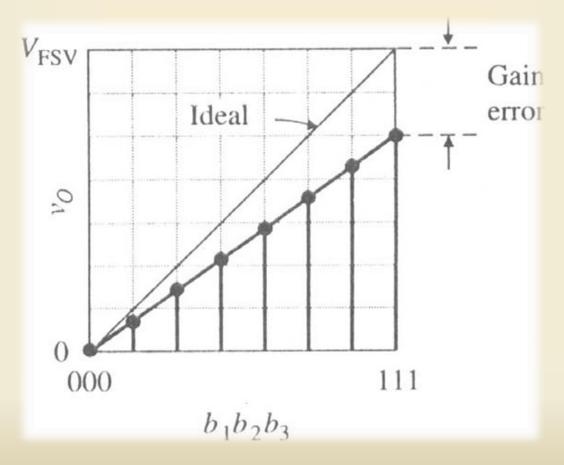

# ERROR DE GANANCIA

D/A

Viene dado por la diferente inclinación en la respuesta

**CONVERTIDORES**

Sensibilidad a la temperatura hace referencia al error producido al variar la temperatura. Se expresa en tanto por ciento del rango de fondo escala.

Monotonicidad es la propiedad según la cual cada incremento de la señal digital de entrada debe producir un incremento del valor de la salida. Cuando esto no ocurre se produce el error de monotonicidad

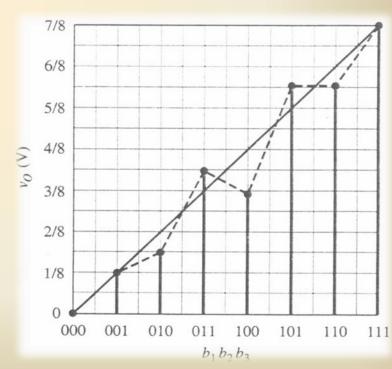

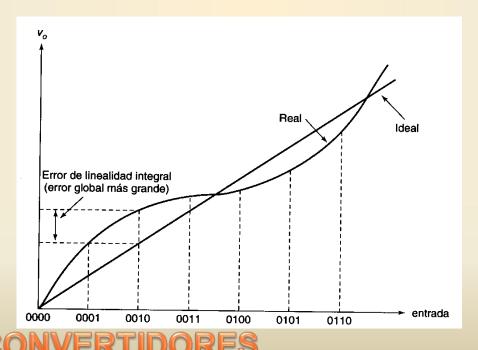

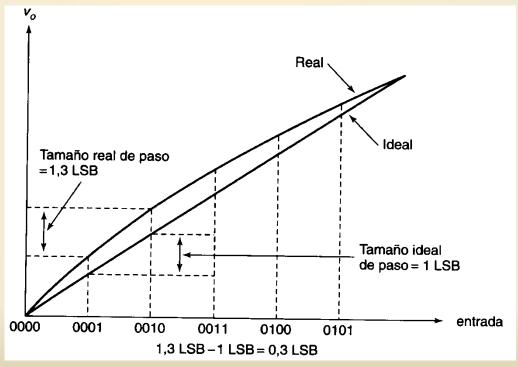

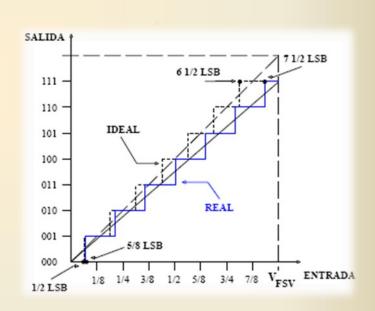

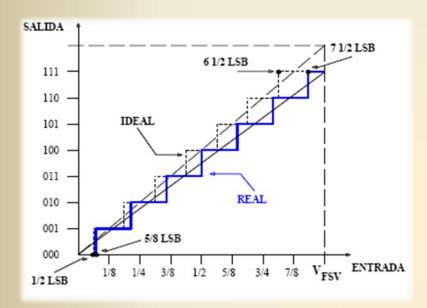

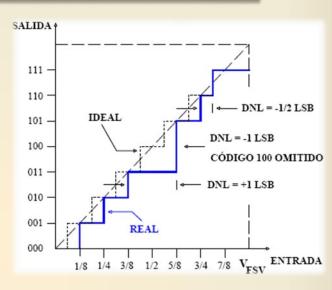

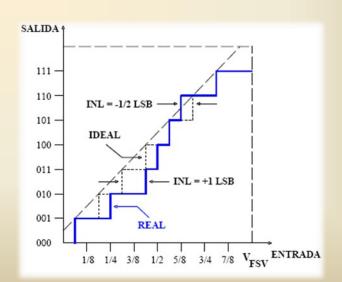

#### ERROR DE NO LINEALIDAD

DIA

Incrementos iguales de entrada deben proporcionar incrementos iguales de salida.

No linealidad integral (INL): Máxima desviación entre la característica de transferencia real e ideal.

No linealidad Diferencial (DNL): Máxima desviación (respecto al ideal) del incremento de Vo entre códigos adyacentes.

# CLASIFICACIÓN DE LOS DACS

DIA

**DE RESISTENCIAS PONDERADAS RESISTIVOS DE ESCALERA R-2R DE CONTROL DE TIEMPO** POR DIVISIÓN DE **ESTOCÁSTICO TENSIÓN DACs** FRECUENCIA-TENSIÓN **EXPONENCIAL**

**CONVERTIDORES**

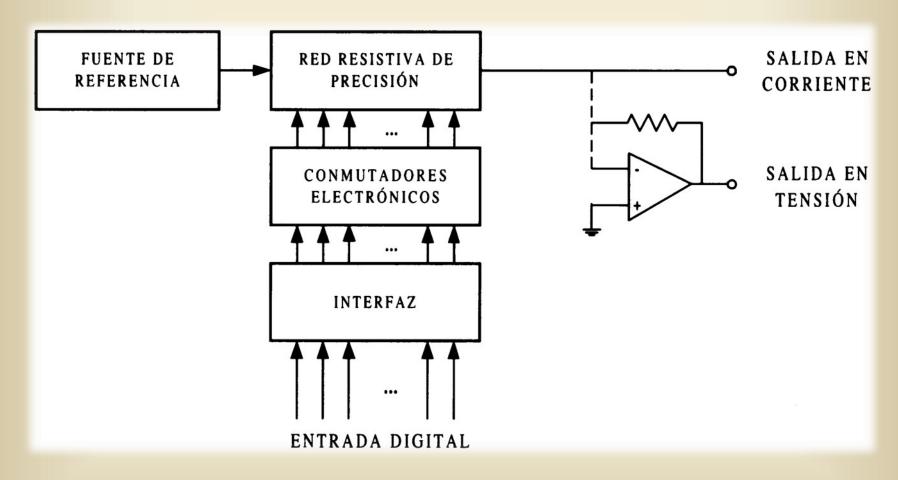

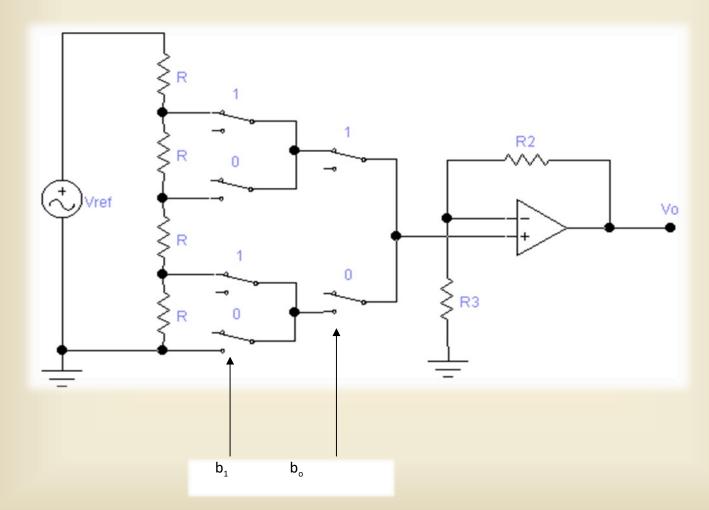

# CONVERTIDOR D/A RESISTIVO

D/A

#### D/A

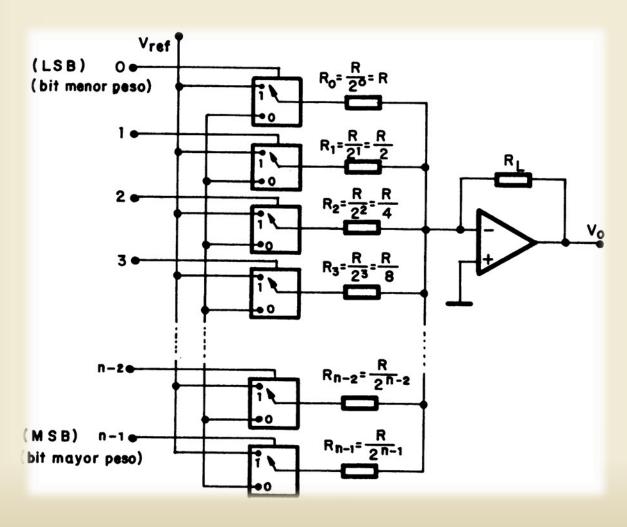

#### DAC DE RESISTENCIAS PONDERADAS

# DAC DE RESISTENCIAS PONDERADAS

D/A

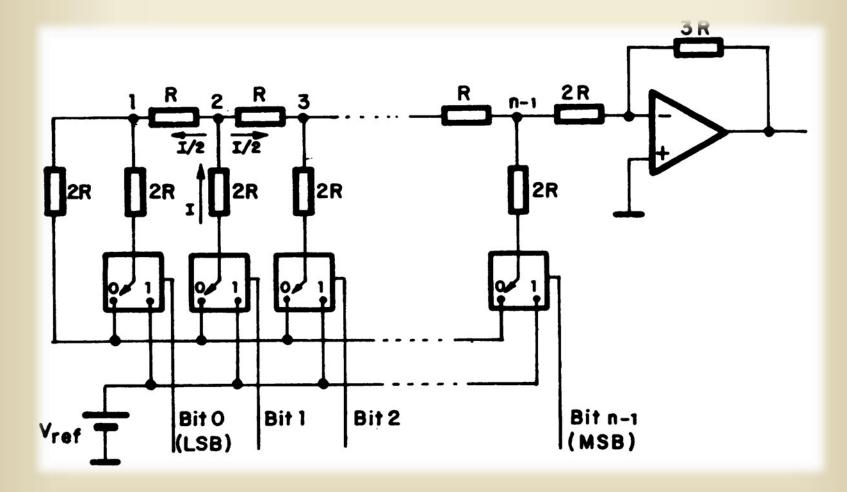

#### DAC DE RED EN ESCALERA R-2R

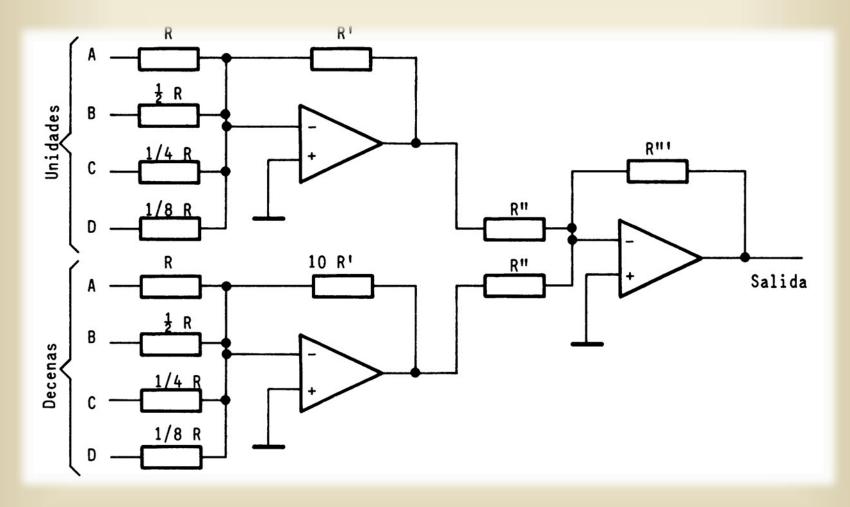

# DAC POR DIVISIÓN DE TENSIÓN

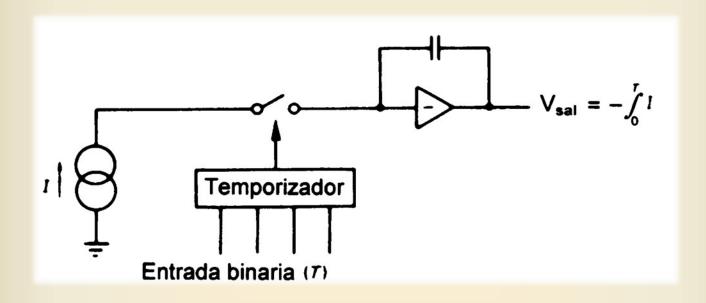

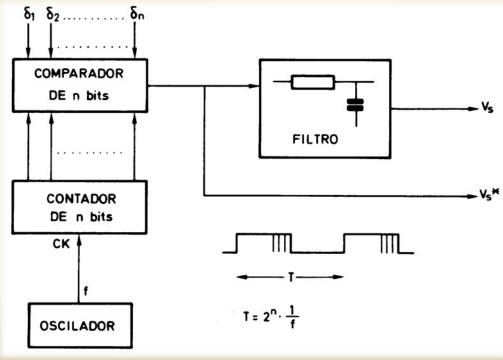

#### DAC POR CONTROL DE TIEMPO

El temporizador varía el tiempo de retención del interruptor en función de la entrada binaria. La salida será de mayor valor cuanto mayor sea el código de entrada.

# CIRCUITO PRÁCTICO

AD

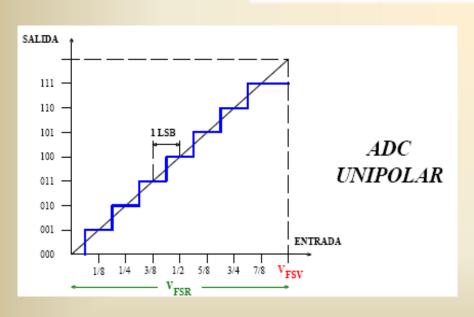

# F. TRANSFERENCIA

DIA

SALIDA DIGITAL EN ORDENADAS

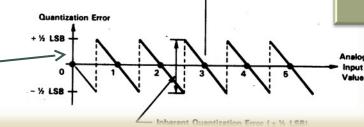

ERROR DE CUANTIFICACIÓN

**EN ABCISAS**

AD

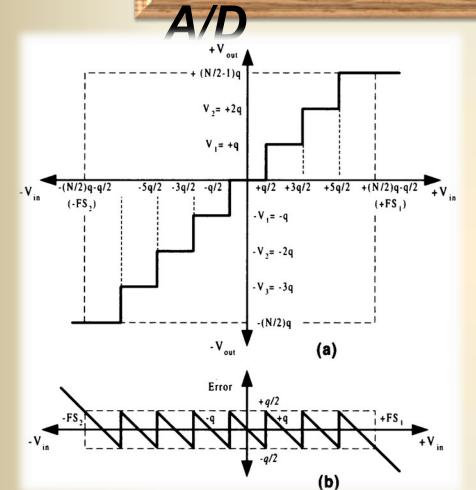

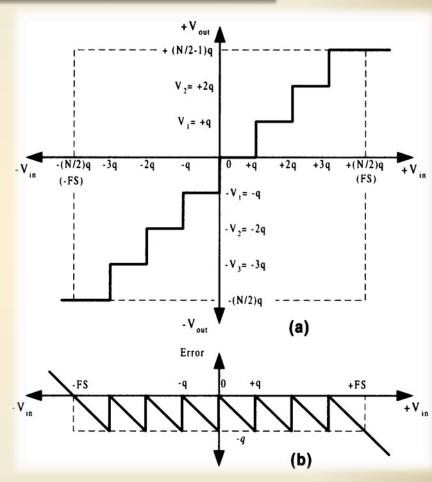

# F. TRANSFERENCIA

CONVERSIÓN POR REDONDEO

CONVERSIÓN POR TRUNCAMIENTO

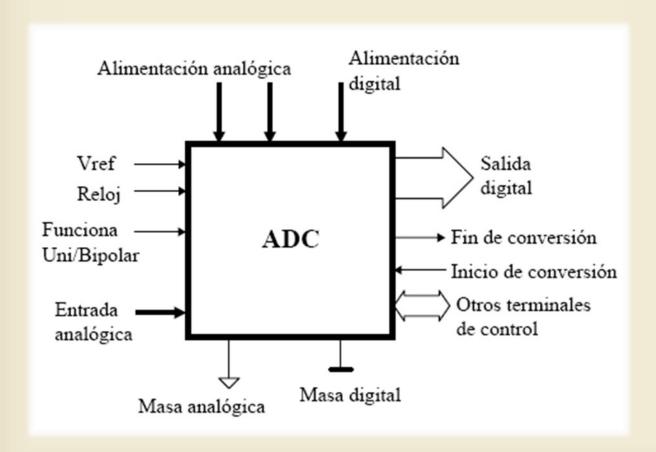

# CARACTERÍSTICAS DE LOS ADCs

Error de offset Resolución o precisión Rango dinámico de Error de ganancia entrada Formato de salida Error de fondo de escala Error de no Tiempo de conversión **linealidad** Integral Tipo de salida **Diferencial** digital De códigos Relación

amitidac

# APRECIACIÓN Y RESOLUCIÓN

Indica el mínimo cambio que se puede detectar de la señal de entrada y se expresa mediante el nº de bits de la palabra código de salida. Viene a tener la misma naturaleza que en los DACs. Puede expresarse en valor absoluto o en tanto por ciento.

$$a = \frac{1}{2^n}.100 (\%)$$

Multiplicado por el fondo de escala nos da la resolución en valor absoluto

| bits | Resolución | V <sub>FSR</sub> =5V |  |  |

|------|------------|----------------------|--|--|

| 8    | 0.39 %     | 19 mV                |  |  |

| 12   | 0.024 %    | 1.22 mV              |  |  |

| 16   | 0.0015 %   | 0.076 mV             |  |  |

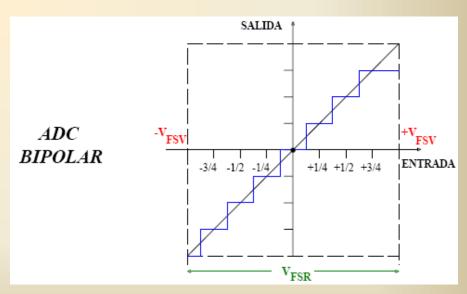

### RANGO DINÁMICO DE ENTRADA

#### Es el margen de tensión máximo a la entrada del convertidor

UNIPOLAR:  $0 \Leftarrow V_I \Rightarrow +V_{FSV}$

BIPOLAR:  $-V_{FSV} \Leftarrow V_{I} \Rightarrow +V_{FSV}$

Indica el código en que se presentan los valores de salida.

En los unipolares los más comunes son:

Binario Natural y

**BCD** natural

En los bipolares se usan:

Binario natural con valor absoluto y signo

Binario en complemento a dos

Binario natural desplazado.

# TIEMPO DE CONVERSIÓN

DIA

Es un dato muy importante, que suele variar entre 10 ns y 10 ms.

Si la tensión de entrada es variable, desde que se inicia la conversión hasta que termina, la tensión de entrada ha cambiado, lo que da lugar al error llamado de apertura.

Para que ese error sea tolerable, la frecuencia máxima de la señal de entrada no debe superar el valor:

$$f_{max} = \frac{1}{2^{n+1} \cdot \pi \cdot Tc}$$

# CARACTERÍSTICAS DE LOS ADCS

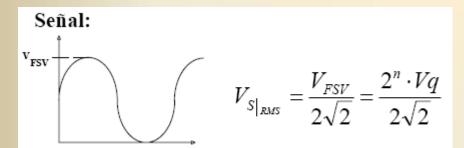

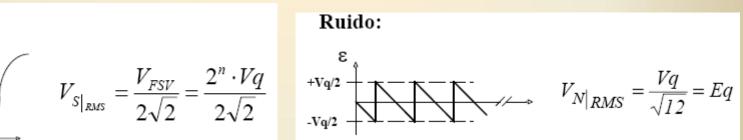

Tipo de salida digital: Ya hemos visto los códigos de salida, esto se refiere a que la salida se puede presentar de otras formas, por ejemplo, con salida serie, salida paralelo, salida multiplexada... Relación señal/ruido: Todos los convertidores presenta errores de cuantificación, que son el ruido. La relación señalruido, medida en decibelios, se expresa como:

$$SNR = \left(\frac{S}{N}\right) = 10 \cdot \log \frac{(V_S)^2}{(V_N)^2} = 6.02 \cdot n + 1.76 \quad dB$$

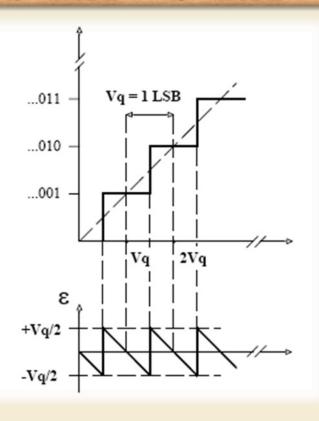

# ERROR DE CUANTIFICACIÓN

DIA

Es inherente a la conversión, puede ser de 1 o de ½ LSB.

Es inevitable

En valor absoluto es menor cuanto mayor sea el número de bits

# CARACTERÍSTICAS DE LOS ADCs

Los errores de offset, ganancia, fondo de escala, y de linealidad tienen son equivalentes a los del DAC.

$$V_{\textit{off}}(\textit{error}) = V_{\textit{t(REAL)}} - V_{\textit{t(IDEAL)}}$$

$$E.G. = (V_{ut} - V_{pt})_{IDEAL} - (V_{ut} - V_{pt})_{REAL}$$

# CARACTERÍSTICAS DE LOS ADCs

$$E.F.ES. = -\frac{7}{8}LSB - \frac{1}{8}LSB = -1LSB$$

AD

# CLASIFICACIÓN DE LOS ADCs

DIA

SIMÉTRICA

**ASIMÉTRICA**

**DE BUCLE** O LAZO **ABIERTO**

**FLASH**

**RAMPA SIMPLE**

**DOBLE RAMPA**

. TRIPLE RAMPA

. DESCARGA

.ENCADENADO

RAMPA EN ESCALERA

CONTINUO

**REGISTRO DE APROXIMACIONES SUCESIVAS**

SIGMA-DELTA

**MODULADOR DE ANCHURA DE PULSO TENSIÓN FRECUENCIA CON COMA FLOTANTE** LOGARÍTMICO

INTERPOLACIÓN-INTEGRACIÓN INTEGRO-POTENCIOMÉTRICO

**ADCs**

**DE BUCLE** O LAZO **CERRADO**

**OTROS TIPOS**

**CONVERTIDORES**

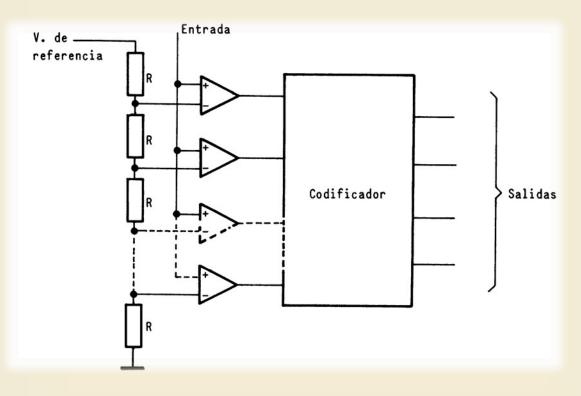

#### ADC DE LAZO ABIERTO

Sobre el esquema, parece la configuración más simple. Tras el proceso de conversión, los valores analógicos de entrada se convierten en valores digitales de salida. El sistema no tiene ningún método de comprobación del resultado, no sabe si la conversión es correcta o no

### **CONVERTIDOR FLASH**

Es llamado convertidor paralelo.

Es el más rápido. Costoso. El número de comparadores es del orden de  $2^{n}$ . Siendo n el número de salidas

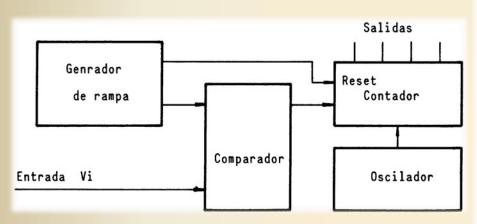

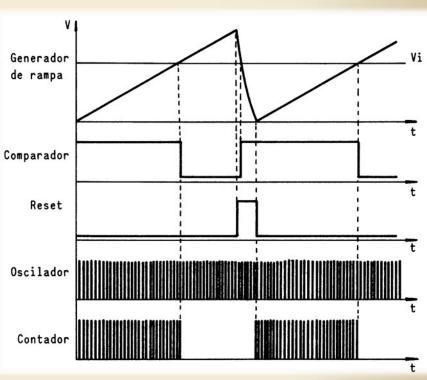

### ADC DE RAMPA SIMPLE

AD

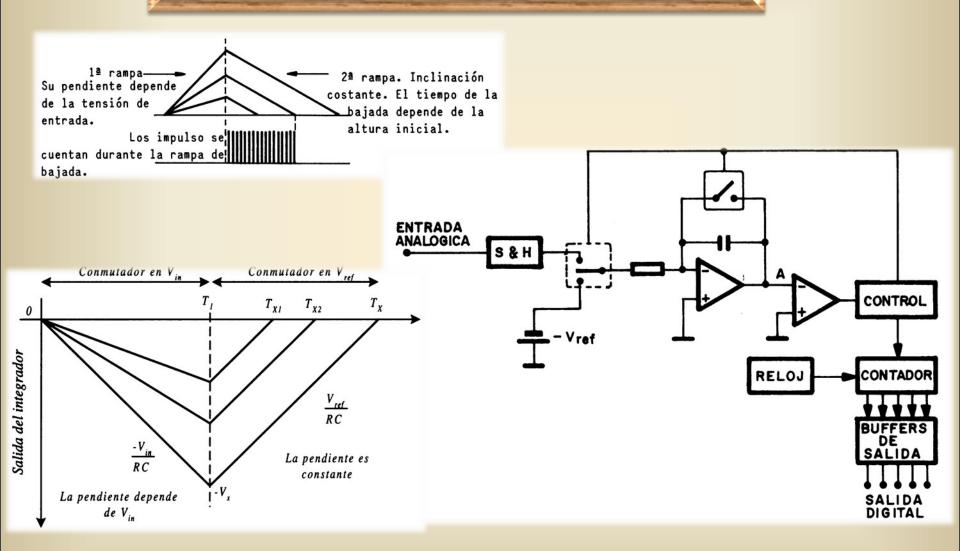

### ADC DE DOBLE RAMPA

DIA

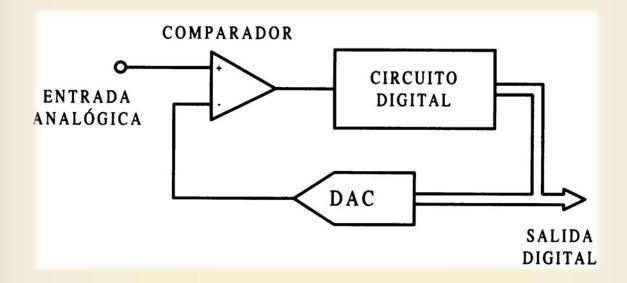

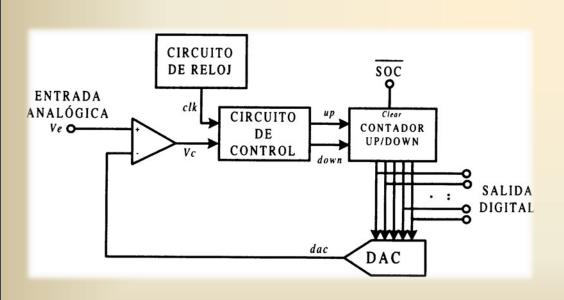

#### ADC DE LAZO CERRADO

Después de realizada la conversión, la salida digital pasa por un convertidor digital-analógico que la vuelve a convertir en analógica.

Estas dos señales se comparan, de forma que la conversión no termina hasta que las dos señales son iguales.

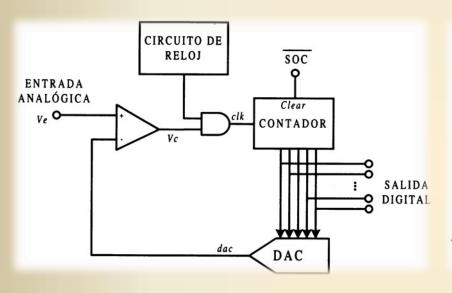

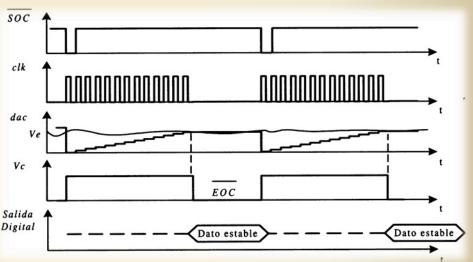

### ADC DE RAMPA EN ESCALERA

Es similar en su filosofía al de rampa simple, pero en lugar de generar una rampa lineal lo hace en escalera con un contador y un DAC.

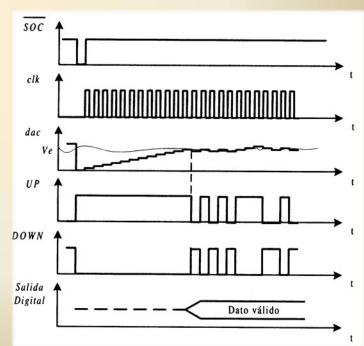

No difiere mucho del anterior. Se sustituye el contador por un contador cuenta-descuenta. De esta forma la salida del comparador decide si el contador debe contar o descontar. Es más rápido que el anterior.

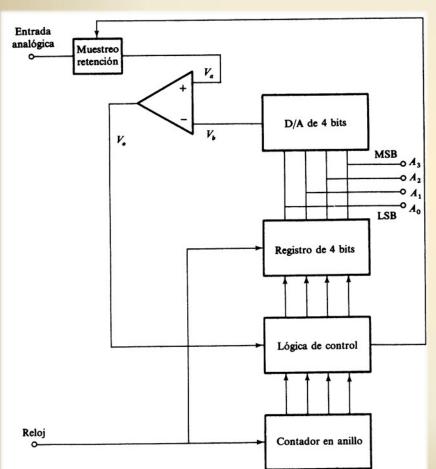

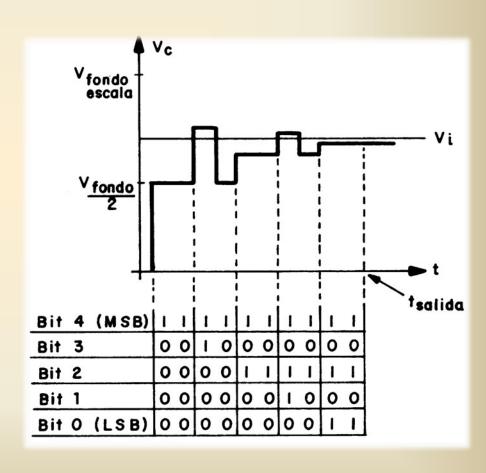

#### ADC DE APROXIMACIONES SUCESIVAS

El elemento diferencial es un Registro de Aproximaciones Sucesivas

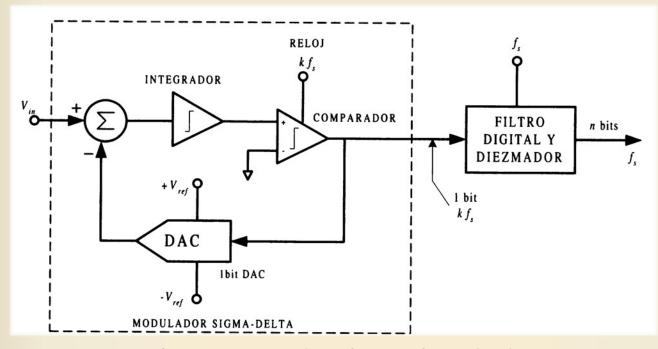

### ADC SIGMA DELTA

Se usa en aplicaciones de alta velocidad y gran número de bits de salida.

La conversión se hace con un solo bit a alta velocidad. El filtro diezmador (o decimador) a la salida amplía el número de bits. La señal de salida puede tener forma de unos y ceros, pero no tener el formato de un código digital. En este caso, la forma de indicar el valor de entrada es variando el ancho del pulso digital de salida. PWM.

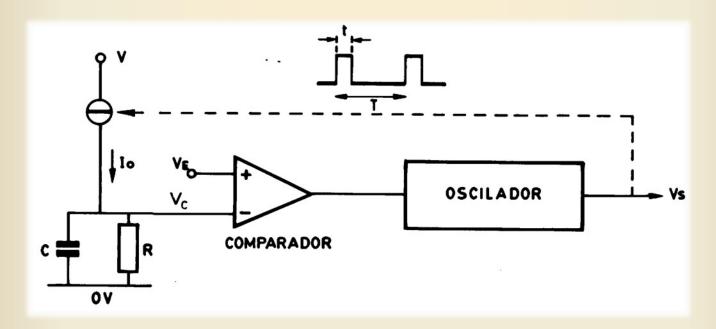

Es una forma de conversión en que la frecuencia de salida es proporcional a la tensión de entrada. Se consigue con un oscilador controlado por tensión.

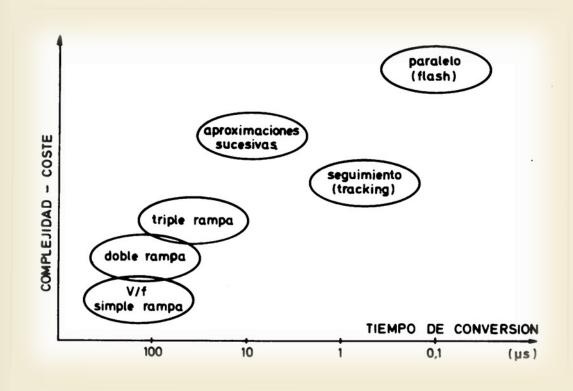

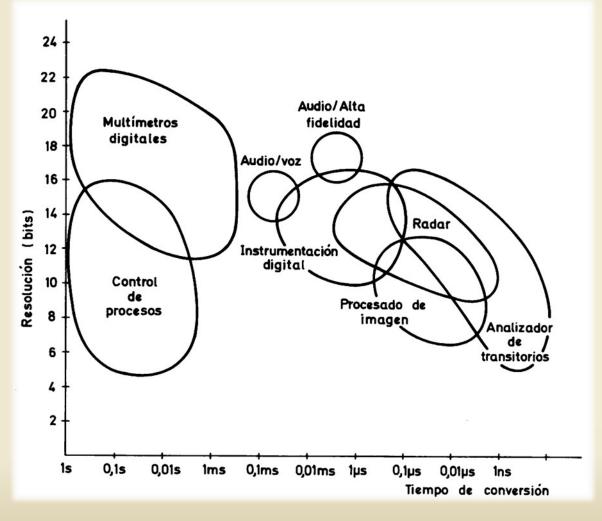

### COMPARATIVA DE CONVERTIDORES

D/A

# CIRCUITO PRÁCTICO

#### EJEMPLO TIPO DE UN DAC DE SONIDO

D/A

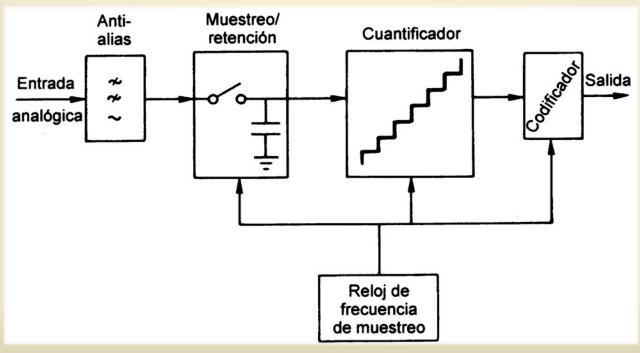

Los circuitos que hemos visto hasta ahora, no son en realidad convertidores, sino solamente una parte de ellos, cuantificadores. Un convertidor para una señal variable puede constar de los siguientes elementos:

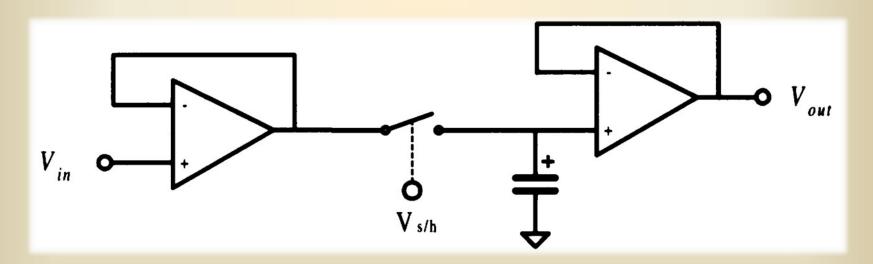

## CIRCUITO DE MUESTREO Y RETENCIÓN

D/A

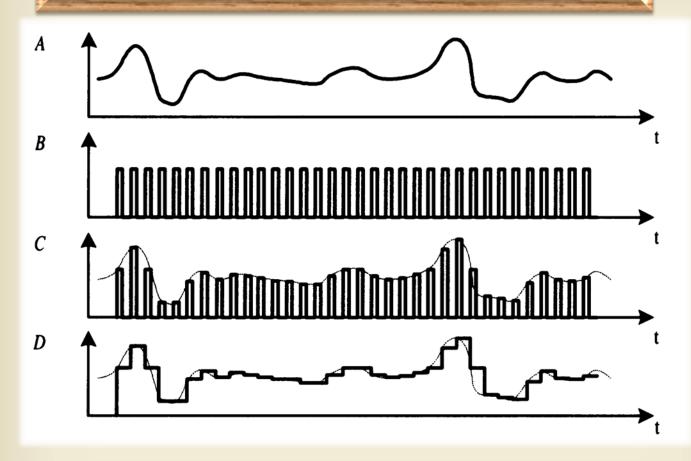

Dado que la señal de entrada está cambiando y que el cuantificador necesita un tiempo para hacer la conversión, lo que hacemos es convertir solamente unos cuantos puntos de la señal, lo que se consigue con un circuito de muestreo y retención.

Según el teorema de Nyquist, para que la señal de salida sea comprensible y reflejo de la entrada, la frecuencia de muestreo debe ser al menos del doble de la máxima frecuencia de entrada.

A/D

### **EFECTO ALIASING**

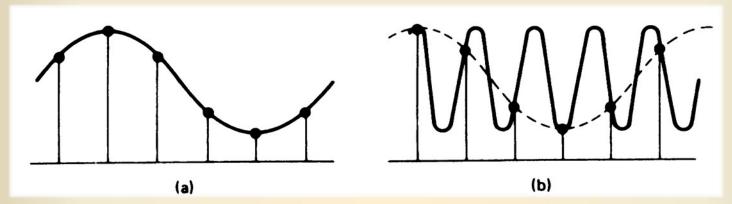

Una señal explorada a intervalos iguales dará lugar a una secuencia de puntos, que unidos deben reproducir aproximadamente la señal original, como ocurre en la señal a.

Si a esos mismos intervalos exploramos una señal de mucha mayor frecuencia, b, la secuencia de puntos explorados pueden darnos una señal muy distinta de la original, es lo que se llama el efecto alias o aliasing.

Para que este efecto no se produzca, la señal de entrada debe ser menor que la mitad de la frecuencia de muestreo (para que cada ciclo de la señal de entrada se entrada se explore al menos dos veces). Por eso en la entrada de los circuitos se pone un filtro (anti alias), que limita la frecuencia de entrada a la mitad de la de muestreo.

# PROCESO DE MUESTREO Y RETENCIÓN

- A.- Señal de entrada

- B.- Frecuencia de muestreo

- C.- Señal muestreada

- D.- Señal retenida

## CRITERIOS DE SELECCIÓN

D/A

A/D

# **CIRCUITOS INTEGRADOS**

DIA

| FABRICANTE               | DENOMINCIÓN | Tc        | BITS A/D | CANAL | BITS D/A | TÉCNICA                 |

|--------------------------|-------------|-----------|----------|-------|----------|-------------------------|

| Analog Devices           | AD570       | 20μs      | 8        | 1     |          | Aprox. Suc.             |

|                          | AD1170      | 1ms       | 12       | 1     |          | Rampa                   |

| Cristal<br>Semiconductor | CS5316      | 62,5µs    | 16       | 1     |          | Delta-Sigma             |

| Ferranti                 | ZN433       | 1μs/bit   | 10       | 1     |          | Seguimiento             |

| Intersil                 | 7109        | 0,1-15Hz  | 12       | 1     |          | Doble rampa             |

| Motorola                 | MC14433     | 300µs     | 8        | 1     |          | Simple rampa            |

| National                 | ADC0808     | 100μs/can | 8        | 8     |          | Aprox.Suc.              |

|                          | ADC1205     | 100µs     | 13       | 8     |          | Mixta                   |

|                          | ADC12181    | 10MHz     | 12       | 1     |          | Pipelined               |

| Texas                    | TLC5503-2   | 25MHz     | 8        | 1     |          | Flash                   |

|                          | TLC1125     | 12µs      | 12+Sig   | 1     |          | RAS                     |

|                          | TCL7135C    | 20ms      | 4½Digit  | 1     |          | Doble rampa             |

| Cirrus Logic             | CS5396      | 100KHz    | 24       | 2     |          | Delta-Sigma             |

| AMD                      | 6080        | 0,16µs    |          | 1     | 8        | Res.Ponder.             |

|                          | 6112        | 7μs       |          | 1     | 12       | Red.Ponder.             |

| Analog Devices           | AD7524      | 0,1 μs    |          | 1     | 8        | R-2R                    |

| GI                       | DAC1600     | 0,3µs     |          | 2     | 10       | Ancho. Pulso            |

| Harris                   | HI5680      | 0,6µs     |          | 1     | 12       | R-2R                    |

| Texas                    | TLC32044M   | 19,2KHz   | 16       | 1     | 14       |                         |

|                          | LM2907      |           |          |       |          | Frecuencia-<br>tensión  |

| TelCom                   | 9400 V/F    |           |          |       |          | Tensión -<br>Frecuencia |

|                          |             |           |          |       |          |                         |